Normal Supply

Normal SupplyAdvanced multi-bus architecture with three independent 16-bit data storage buses and one program storage bus

A 40-bit arithmetic logic unit (ALU) consisting of a 40-bit bucket shifter and two separate 40-bit accumulators

17× 17-bit parallel multiplier coupled with 40-bit dedicated adder,

for non-pipelined single-period product/add (MAC) operations

Comparison, Selection, and Storage Units (CSSU) for the accumulation/comparison selection of Viterbi operators

In one cycle, the index encoder is used to calculate the index value of a 40 bit accumulator

Two address generators with eight auxiliary registers and two auxiliary register arithmetic units (ARAUs)

A data bus with bus hold function

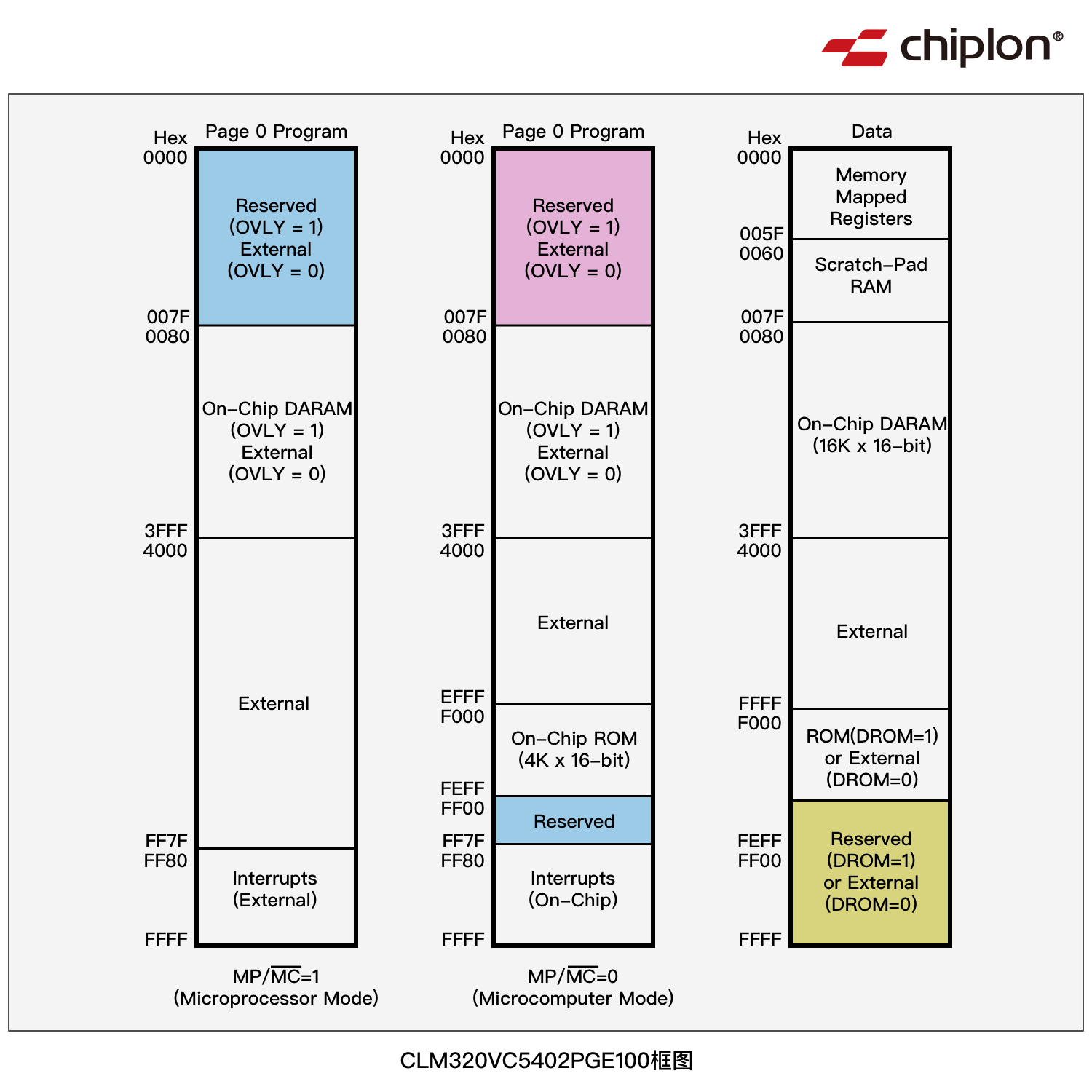

A maximum addressable external program space of 1M x 16 bits

Extended Addressing Mode

4K × 16 bit on-chip ROM (Read Only Memory)

16K x 16 bit dual access on-chip RAM (random access memory)

Single instruction repeat and block repeat operation program code

Block memory move instructions for efficient programming and data management

Instructions with 32-bit word operands

Instructions with 2/3 operands read

Chiplon introduces digital signal processor (DSP) products for industrial applications, the CLM320VC5402 is an advanced multi-bus architecture, with three independent 16-bit data storage bus and one program storage bus 16-bit fixed-point digital signal processor. Direct Pin-to-pin replacement of international similar products, without changing the circuit board or system software, to achieve full replacement compatibility. Chiplon Microelectronics has developed its own testing plan to ensure that the factory products meet or even exceed the original specifications, supporting industrial grade (-40 ℃~100 ℃) operating temperatures.Competitor product: TMS320VC5402PGE100

Advanced multi-bus architecture with three independent 16-bit data storage buses and one program storage bus

A 40-bit arithmetic logic unit (ALU) consisting of a 40-bit bucket shifter and two separate 40-bit accumulators

17× 17-bit parallel multiplier coupled with 40-bit dedicated adder,

for non-pipelined single-period product/add (MAC) operations

Comparison, Selection, and Storage Units (CSSU) for the accumulation/comparison selection of Viterbi operators

In one cycle, the index encoder is used to calculate the index value of a 40 bit accumulator

Two address generators with eight auxiliary registers and two auxiliary register arithmetic units (ARAUs)

A data bus with bus hold function

A maximum addressable external program space of 1M x 16 bits

Extended Addressing Mode

4K × 16 bit on-chip ROM (Read Only Memory)

16K x 16 bit dual access on-chip RAM (random access memory)

Single instruction repeat and block repeat operation program code

Block memory move instructions for efficient programming and data management

Instructions with 32-bit word operands

Instructions with 2/3 operands read

Smart speaker

Thermostat

Digital stethoscope

Land Mobile Radio

Visual doorbell